| СОГЛАСОВАНО<br>Начальник 166 ВП МО РФ | УТВЕРЖДАЮ<br>Генеральный директор |  |  |  |

|---------------------------------------|-----------------------------------|--|--|--|

|                                       | OAO «СКТБ ЭС»                     |  |  |  |

| С.И. Перов<br>«»2006 г.               | И.Е. Лобов                        |  |  |  |

| 20001.                                | «»2006 r                          |  |  |  |

|                                       |                                   |  |  |  |

|                                       |                                   |  |  |  |

|                                       |                                   |  |  |  |

|                                       |                                   |  |  |  |

| МИКРОСХЕМА 1                          | ИНТЕГРАЛЬНАЯ                      |  |  |  |

| 1273ΠA2T,                             | 1273ΠΑ2ΑΤ                         |  |  |  |

| Техническо                            | ое описание                       |  |  |  |

| ГКЛЯ.431                              | 320.003TO                         |  |  |  |

|                                       |                                   |  |  |  |

|                                       |                                   |  |  |  |

|                                       |                                   |  |  |  |

|                                       |                                   |  |  |  |

|                                       |                                   |  |  |  |

| СОГЛАСОВАНО                           |                                   |  |  |  |

| Руководитель группы ВП                | Главный конструктор ОКР           |  |  |  |

| Ю.П. Петров                           | С.М. Кононов                      |  |  |  |

| «»2006 г.                             | «»2006 г.                         |  |  |  |

|                                       | Нормоконтроль                     |  |  |  |

|                                       | Н.И. Васина                       |  |  |  |

|                                       | «»2006 г.                         |  |  |  |

Инв. № дубл.

Взам. инв №

Инв. № подл.

# Содержание

|               | 1 Введение                                                  | 3  |

|---------------|-------------------------------------------------------------|----|

|               | 2 Назначение                                                | 4  |

|               | 3 Основные технические характеристики                       | 5  |

|               | 4 Условное обозначение и назначение выводов ИС              | 8  |

|               | 5 Устройство и работа ИС                                    | 10 |

|               | 5.1 Блок-схема.                                             | 10 |

|               | 5.2 Блок цифро-аналогового преобразования                   | 12 |

|               | 5.3 Выходной усилитель                                      | 12 |

|               | 5.4 Входное опорное напряжение                              | 13 |

|               | 5.5 Фильтрация напряжения питания и требования к выполнению |    |

|               | проводников «земли».                                        | 15 |

|               | 5.6 Входные каскады цифровых сигналов                       | 16 |

| дата          | 5.7 Цифровой интерфейс                                      | 17 |

| Подп. и дата  | 5.8 Сигнал сброса RS#                                       | 18 |

| IIc           | 5.9 Дежурный режим                                          | 19 |

|               | 5.10 Использование микросхем в однополярном режиме          | 20 |

| <u>е</u> дуб. | 5.11 Использование микросхем в биполярном режиме            | 21 |

| Инв. № дубл   |                                                             |    |

| <u> </u>      |                                                             |    |

| HB.           |                                                             |    |

#### 1 Введение

Настоящее техническое описание предназначено для изучения интегральных микросхем 1273ПА2Т, 1273ПА2АТ содержит описание принципа их работы, технические характеристики и другие сведения, необходимые для обеспечения полного использования технических возможностей микросхем.

| Подп. и дата |  |

|--------------|--|

| Инв. № дубл. |  |

| Взам. Инв. № |  |

| Подп. и дата |  |

| Инв. № подл. |  |

#### 2 Назначение

Интегральные микросхемы 1273ПА2Т, 1273ПА2АТ АЕЯР.431320.472ТУ – это 12-разрядные цифро-аналоговые преобразователи, с 12-разрядным параллельным интерфейсом. Микросхемы предназначены для преобразования сигналов из цифровой формы в аналоговую (напряжение) с временем установления выходного сигнала не превышающим 130 мкс – для ИС 1273ПА2Т и не превышающим 200 мкс – для ИС 1273ПА2АТ (в диапазоне температур).

ЦАП может быть легко встроен в любую микропроцессорную систему, особенно просто, если микропроцессор имеет параллельный порт.

|              | Ī |

|--------------|---|

| Подп. и дата |   |

| Инв. № дубл. |   |

| Взам. Инв. № |   |

| Подп. и дата |   |

| Инв. № подл. |   |

# 3 Основные технические характеристики

3.1 Значения электрических параметров микросхем 1273ПА2Т, 1273ПА2АТ приведены в таблице 1.

Таблица 1 – Электрические параметры микросхем

| Наименование параметра,                                                                                                                             | Букранцоа                           | Буквенное Норма па |             |             | параметра   |                        |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------------|-------------|-------------|-------------|------------------------|--|

| единица измерения, режим измерения                                                                                                                  | обозна-                             | зна- 1273ПА2Т      |             | 1273ПА2АТ   |             | Темпе-                 |  |

| P                                                                                                                                                   | параметра                           | не<br>менее        | не<br>более | не<br>менее | не<br>более | среды, °С              |  |

| 1                                                                                                                                                   | 2                                   | 3                  | 4           | 5           | 6           | 7                      |  |

| Смещение, мВ при 2,7 В $\leq$ U <sub>CC</sub> $\leq$ 5,5 В, U <sub>REF</sub> = 2,5 В, Входные данные = $000_{\rm H}$                                | Uoo                                 | _                  | 4,0         | _           | 4,0         | 25±10<br>85±3          |  |

| Бходные данные – 000н                                                                                                                               |                                     | _                  | 8,0         | ı           | 8,0         | -60±3                  |  |

| Погрешность в конечной точке характеристики преобразования, мВ                                                                                      | $E_G$                               | -8,0               | 8,0         | -8,0        | 8,0         | 25±10<br>85±3          |  |

| при 2,7 B $\leq$ U <sub>CC</sub> $\leq$ 5,5 B, U <sub>REF</sub> = 2,5 B, Входные данные = FFF <sub>H</sub>                                          |                                     | -20,0              | 20,0        | -20,0       | 20,0        | -60±3                  |  |

| Выходной вытекающий ток, мА при 2,7 B $\leq$ U <sub>CC</sub> $\leq$ 5,5 B, Входные данные = $800_{\rm H}$                                           | I <sub>O1</sub>                     | 1,0                | _           | 1,0         | _           | 25±10<br>-60±3<br>85±3 |  |

| Выходной втекающий ток, мА при 2,7 B $\leq$ U <sub>CC</sub> $\leq$ 5,5 B,                                                                           | $I_{O2}$                            | 3,0                | _           | 2,7         | _           | 25±10<br>-60±3         |  |

| Входные данные = 800н                                                                                                                               |                                     | 3,0                | _           | 2,1         | _           | 85±3                   |  |

| Входной ток высокого и низкого уровней, мкА при $U_{IH} = U_{CC},  U_{IL} = 0  B,$ 2,7 $B \le U_{CC} \le 5,5  B$                                    | I <sub>IH,</sub><br>I <sub>IL</sub> | -8,0               | 8,0         | -8,0        | 8,0         | 25±10<br>-60±3<br>85±3 |  |

| Ток потребления, мкА при $2.7~\mathrm{B} \leq \mathrm{U_{CC}} \leq 5.5~\mathrm{B},$ Входные данные = $000_\mathrm{H},$ Внешняя нагрузка отсутствует | I <sub>CC</sub>                     | _                  | 100         | -           | 120         | 25±10<br>-60±3<br>85±3 |  |

| Ток потребления в режиме SHDN ("дежурный режим"), мкА $2.7~B \le U_{CC} \le 5.5~B$ , Входные данные = $000_{H}$ , Внешняя нагрузка отсутствует      | I <sub>CC_SHDN</sub>                | -                  | 1,5         | -           | 1,5         | 25±10<br>-60±3<br>85±3 |  |

# Окончание таблицы 1

| 1                                                                                                                 | 2                   | 3    | 4     | 5    | 6     | 7                      |

|-------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|------|-------|------------------------|

| Время установления выходного напряжения, мкс                                                                      | ts                  | -    | 130,0 | -    | 150,0 | 25±10<br>85±3          |

| при 2,7 В ≤ U <sub>CC</sub> ≤ 5,5 В                                                                               |                     | _    | 130,0 | _    | 200,0 | -60±3                  |

| Время выхода из режима SHDN ("дежурный режим"), мкс                                                               | t <sub>S_SHDN</sub> | ı    | 150,0 | ı    | 170,0 | 25±10<br>85±3          |

| при 2,7 В ≤ U <sub>CC</sub> ≤ 5,5 В                                                                               |                     | I    | 150,0 | I    | 250,0 | -60±3                  |

| Нелинейность*, MP при $2.7~\mathrm{B} \leq \mathrm{U_{CC}} \leq 5.5~\mathrm{B},\mathrm{U_{REF}} = 2.5~\mathrm{B}$ | $E_{L01}$           | -1,8 | 1,8   | -1,8 | 1,8   | 25±10                  |

|                                                                                                                   |                     | -3,0 | 3,0   | -3,0 | 3,0   | -60±3<br>85±3          |

| Дифференциальная нелинейность*, MP при 2,7 B $\leq$ U <sub>CC</sub> $\leq$ 5,5 B, U <sub>REF</sub> = 2,5 B        | E <sub>LD</sub>     | -0,9 | 0,9   | -0,9 | 0,9   | 25±10                  |

| Число разрядов, бит при 2,7 B $\leq$ U <sub>CC</sub> $\leq$ 5,5 B                                                 | n                   | 12   | _     | 12   | _     | 25±10<br>-60±3<br>85±3 |

$<sup>^*</sup>$ без учёта выходных значений ЦАП для первых двух кодов входных данных:  $000_{\rm H},\,001_{\rm H}.$

3.2 Предельно-допустимые режимы эксплуатации микросхем 1273ПА2Т, 1273ПА2АТ приведены в таблице 2.

Таблица 2 – Предельно допустимые и предельные режимы эксплуатации микросхем

| Наименование<br>параметра режима,          | Буквенное<br>обозначение | бозначение допустимый пежим |                        | Предельный<br>режим |                      |

|--------------------------------------------|--------------------------|-----------------------------|------------------------|---------------------|----------------------|

| единица измерения                          | параметра                | не<br>менее                 | не<br>более            | не<br>менее         | не<br>более          |

| 1                                          | 2                        | 3                           | 4                      | 5                   | 6                    |

| Напряжение питания, В                      | $U_{CC}$                 | 2,7                         | 5,5                    | -0,3                | 8,0                  |

| Опорное напряжение, В                      | $U_{ m REF}$             | 0                           | $U_{CC}$               | -0,3                | U <sub>CC</sub> +0,3 |

| Входное напряжение низкого уровня, В       | $U_{\mathrm{IL}}$        | 0                           | 0,5 (3 B)<br>0,8 (5 B) | -0,3                | -                    |

| Входное напряжение высокого уровня*, В     | U <sub>IH</sub>          | U <sub>CC</sub> -0,6        | $U_{CC}$               | -                   | U <sub>CC</sub> +0,3 |

| Длительность сигнала выбора кристалла*, нс | t <sub>W_CS</sub>        | 45                          | -                      | -                   | -                    |

| Время установления<br>входных данных*, нс  | t <sub>SU_D</sub>        | 30 (3 B)<br>15 (5 B)        | -                      | -                   | -                    |

| Время удержания<br>входных данных*, нс     | t <sub>H_D</sub>         | 20 (3 B)<br>5 (5 B)         | -                      | -                   | -                    |

| Длительность импульса сброса, нс           | t <sub>W_RS</sub>        | 40 (3 B)<br>30 (5 B)        | -                      | -                   | -                    |

| Максимальная рассеиваемая мощность, мВт    | $P_{tot}$                | -                           | 0,5                    | -                   | -                    |

| Ёмкость нагрузки, пФ                       | $C_{L}$                  | -                           | 100,0**                |                     |                      |

$<sup>^*</sup>$  Предельно-допустимые значения параметров  $t_{W\_CS}$ ,  $t_{SU\_D}$ ,  $t_{H\_D}$ ,  $t_{W\_RS}$  устанавливаются при длительностях фронтов/спадов входных сигналов не более 2 нс.

$<sup>^{**}</sup>$  Допускается эксплуатация с ёмкостью нагрузки до 200 пФ, при этом динамические параметры микросхемы при ёмкости нагрузки более 100 пФ не гарантируются.

# 4 Условное графическое обозначение и назначение выводов ИС

DIN

4.1 Условное графическое обозначение микросхем приведено на рисунке 1.

DAC

| 5 DIN0 6 DIN1                                     |    |

|---------------------------------------------------|----|

|                                                   |    |

| 7                                                 |    |

| 7 DIN2                                            |    |

| 8 DIN3                                            |    |

| 9 DIN4                                            |    |

| 10 DIN5                                           |    |

| 11 DIN6                                           |    |

| 12 DIN7                                           |    |

| 13 DIN8                                           |    |

| $\overline{}$ DIN9 $\overline{}$ V <sub>OUT</sub> | 19 |

| 15 DIN10                                          | Ĭ  |

| 16 DIN11                                          |    |

|                                                   |    |

| 3CS#                                              |    |

| 4 RS#                                             |    |

|                                                   |    |

|                                                   |    |

| $v_{ m REF}$                                      |    |

| 1 V <sub>CC</sub>                                 |    |

| 18AGND                                            |    |

| 17DGND                                            |    |

| i                                                 |    |

Рисунок 1 – Условное графическое обозначение ИС 1273ПА2Т, 1273ПА2АТ

#### 4.2 Назначение выводов микросхем приведено в таблице 3.

Таблица 3 – Назначение выводов микросхем 1273ПА2Т, 1273ПА2АТ

| вывода | Обозначение  | Назначение вывода                                                                                                                                                                                                         |

|--------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | $V_{CC}$     | Напряжение питания микросхемы                                                                                                                                                                                             |

| 2      | SHDN#        | Логический вход сигнала перевода ИС в дежурный режим (очень низкого энергопотребления). Активный уровень сигнала – низкий. В дежурном режиме сохраняется функция хранения во входном регистре ЦАП и функция записи в него |

| 3      | CS#          | Логический вход сигнала выбора кристалла. Активный уровень – низкий                                                                                                                                                       |

| 4      | RS#          | Логический вход сигнала сброса входных регистров ЦАП в нулевое состояние. Активный уровень – низкий                                                                                                                       |

| 5      | DIN0         | Логический вход данных, 0 разряд                                                                                                                                                                                          |

| 6      | DIN1         | Логический вход данных, 1 разряд                                                                                                                                                                                          |

| 7      | DIN2         | Логический вход данных, 2 разряд                                                                                                                                                                                          |

| 8      | DIN3         | Логический вход данных, 3 разряд                                                                                                                                                                                          |

| 9      | DIN4         | Логический вход данных, 4 разряд                                                                                                                                                                                          |

| 10     | DIN5         | Логический вход данных, 5 разряд                                                                                                                                                                                          |

| 11     | DIN6         | Логический вход данных, 6 разряд                                                                                                                                                                                          |

| 12     | DIN7         | Логический вход данных, 7 разряд                                                                                                                                                                                          |

| 13     | DIN8         | Логический вход данных, 8 разряд                                                                                                                                                                                          |

| 14     | DIN9         | Логический вход данных, 9 разряд                                                                                                                                                                                          |

| 15     | DIN10        | Логический вход данных, 10 разряд                                                                                                                                                                                         |

| 16     | DIN11        | Логический вход данных, 11 разряд                                                                                                                                                                                         |

| 17     | DGND         | "Земля" цифровой части микросхемы                                                                                                                                                                                         |

| 18     | AGND         | "Земля" аналоговой части микросхемы                                                                                                                                                                                       |

| 19     | $V_{ m OUT}$ | Выход аналогового напряжения ЦАП                                                                                                                                                                                          |

| 20     | $V_{ m REF}$ | Аналоговый вход опорного напряжения ЦАП                                                                                                                                                                                   |

Номер

#### 5 Устройство и работа ИС

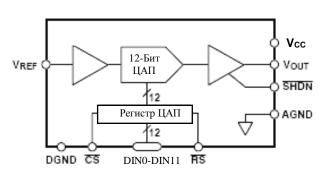

#### 5.1 Блок-схема ИС приведена на рисунке 2.

Рисунок 2 – Блок-схема ИС 1273ПА2Т, 1273ПА2АТ

ИС 1273ПА2Т, 1273ПА2АТ – это 12-разрядный цифро-аналоговый преобразователь с выходным сигналом в виде напряжения. ИС разработана для работы от одного источника питания плюс 3 В/5 В. Микросхемы выполнены по БИ-КМОП технологии. Функционирование гарантируется при питания от 2,7 В до 5,5 В, что идеально подходит для применения в системах с батарейным питанием. Выходное напряжение полной шкалы определяется входным напряжением, подаваемым на вход  $V_{REF}$ . Так как, допустимый диапазон напряжений для  $V_{REF}$ : от 0 до  $U_{CC}$ , то напряжение полной шкалы на выходе ЦАП может быть равно  $U_{CC}$  или любому значению от 0 B до  $U_{CC}$ .

12-разрядный регистр-защелка данных с временем записи 45 нс позволяет осуществлять связь ЦАП с самыми быстрыми процессорами без тактов ожидания.

Асинхронный сигнал сброса RS# устанавливает на выходе напряжение, соответствующее нулю шкалы при подаче питания или, когда это задается пользователем.

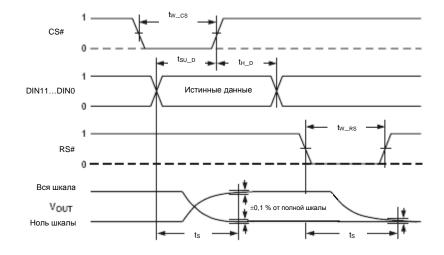

Временная диаграмма входных логических сигналов, соблюдение которой гарантирует нормальное функционирование, и сигнала выходного напряжения приведена на рисунке 3.

Рисунок 3 — Временная диаграмма входных логических сигналов ИС

Итак, ИС 1273ПА2Т, 1273ПА2АТ – это 12-разрядный цифро-аналоговый преобразователь. Ток потребления ИС не превышает 100 мкА, что позволяет использовать его в системах с батарейным питанием. ЦАП состоит из 12-ти ключей, управляемых напряжением, собственно, цифро-аналогового преобразователя с лазерной подгонкой, выходного операционного усилителя с диапазоном выходного сигнала равным напряжению питания (rail-to-rail) и входного параллельного регистра. Вход внешнего опорного напряжения  $V_{\text{REF}}$ имеет постоянное входное сопротивление, независимое от входного цифрового кода ЦАП. Вход V<sub>REF</sub> может быть подключен к источнику напряжения питания U<sub>CC</sub> – результатом будет максимальный микросхемы размах напряжения: от 0 В до U<sub>CC</sub>. Входной параллельный интерфейс состоит из 12-ти линий данных DIN0 – DIN11 и строб-сигнала записи CS#. Имеется, также, вход сброса RS# для установления выхода ЦАП в нуль шкалы. Сброс полезен при включении питания, а также для установки системы в исходное состояние в случае сбоя в работе. Дополнительным средством сохранения энергии является дежурный режим работы микросхемы, который может быть включен активацией сигнала SHDN#. В этом режиме ИС потребляет 1,5 мкА максимум. Если питание ИС остается включенным, выходное напряжение ЦАП восстанавливается, как только сигнал SHDN# возвращается на пассивный уровень (высокий).

№ подл.

Ниже приведена таблица истинности функционирования входного интерфейса.

Таблица 4 - Таблица истинности функционирования входного интерфейса

| CS#      | RS#     | Регистр ЦАП               |

|----------|---------|---------------------------|

| Высокий  | Высокий | Без изменения             |

| Низкий   | Высокий | Отображает входные данные |

| <b>↑</b> | Высокий | Фиксирует входные данные  |

| X        | Низкий  | Очищается (все нули)      |

| Высокий  | 1       | Фиксирует все нули        |

#### 5.2 Блок цифро-аналогового преобразования

ЦАП на основе резистивной матрицы R–2R и ключей, переключаемых напряжением, генерирует выходное напряжение, которое является функцией опорного напряжения и входного цифрового кода. Выходное напряжение равно:

$$U_{OUT} = U_{REF} \times D/2^N$$

,

где D — это десятичное значение входного двоичного кода, загруженного в регистр ЦАП;

N = 12 -разрядность ЦАП.

Если опорное напряжение равно 5 B, то номинальное выходное напряжение середины шкалы будет равно 2,5 B при цифровом коде D = 2048, а напряжение полной шкалы равно 4,9988 B. Величина  $EMP = 5.0 \times 1/4096 = 0.0012$  B.

## 5.3 Выходной усилитель

Внутренний выход ЦАП подключен к буферному прецизионному усилителю с малым потреблением. Операционный усилитель имеет типовое время установления (с точностью 0,1 % от полной шкалы) 120 мкс. Имеется небольшая разница во временах установления при спадающих выходных напряжениях и

Подп. и дата

Инв. № дубл.

Взам. Инв. №

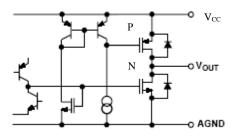

нарастающих. Плюс к сказанному, при ниспадающих выходных напряжениях время установления в пределах последних 6-ти ЕМР близ нуля вольт несколько возрастает. Выходной каскад усилителя разработан так, чтобы была обеспечена заданная точность функционирования около обоих крайних значений напряжения питания (rail-to-rail). На рисунке 4 приведена эквивалентная схема такого выходного каскада. Здесь используется N-канальный полевой транзистор, который обеспечивает «притяжение» напряжения на нагрузке непосредственно к уровню GND. Выходной вытекающий ток обеспечивает Р-канальный транзистор, который может выдать ток в нагрузку, соединенную с GND. Выходной каскад обеспечивает диапазон выходного напряжения равный напряжению питания (rail-to-rail).

Нижний N-канальный полевой транзистор в открытом состоянии имеет сопротивление 35 Ом, вследствие чего, втекающий ток обеспечивает выходное напряжение близкое к нулю. Кроме обеспечения управления резистивной нагрузкой, усилитель ориентирован на управление емкостной нагрузкой до 100 пФ.

Подп. и дата

Инв. № дубл.

Взам. Инв. №

Подп. и дата

№ подл.

Рисунок 4 - Эквивалентная схема выходного каскада усилителя

# 5.4 Входное опорное напряжение

Входное сопротивление цепи опорного напряжения  $V_{REF}$  постоянно и не зависит от цифрового кода. Как результат, уменьшается влияние на источник опорного напряжения. Высокое входное сопротивление (2,5 МОм) по входу  $V_{REF}$  минимизирует ток потребления ЦАП. Допустимые значения входного опорного

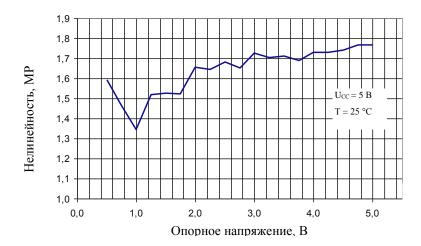

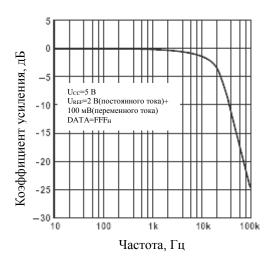

напряжения лежат в диапазоне от 0 B до напряжения питания U<sub>CC</sub>. В простейшем варианте вход V<sub>REF</sub> подключается к напряжению питания U<sub>CC</sub>. Такое соединение обеспечивает размах выходного напряжения равный напряжению питания. На вход опорного напряжения может подаваться сигнал напряжения переменного тока, при условии, что его значения не будут выходить за пределы напряжения питания, то есть, при условии соблюдения неравенства:  $0 \le U_{REF} \le U_{CC}$ . На рисунках 5, 6 приведены типовые зависимости нелинейности ЦАП 1273ПА2Т, 1273ПА2АТ от величины опорного напряжения и коэффициента передачи ЦАП 1273ПА2Т, 1273ПА2АТ от частоты сигнала опорного напряжения переменного тока.

Рисунок 5 - Зависимость нелинейности от величины опорного напряжения

Рисунок 6 - Зависимость коэффициента передачи от частоты сигнала опорного напряжения переменного тока

№ подл.

Подп. и дата

Инв. № дубл.

윋

Взам. Инв.

# 5.5 Фильтрация напряжения питания и требования к выполнению проводников «земли»

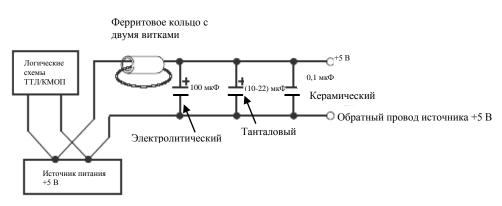

Прецизионные аналоговые приборы, каковыми являются ЦАП 1273ПА2Т, 1273ПА2АТ требуют тщательной фильтрации напряжения питания. Учитывая то, что ЦАП функционирует при напряжении питания от 2,7 В до 5,5 В, может показаться удобным использовать источник питания цифровых логических схем. сожалению, логические схемы часто работают в ключевых режимах, в результате чего генерируют шум в полосе от 20 кГц до 1 МГц. Кроме того, логические вентили ΜΟΓΥΤ генерировать выбросы напряжения сопротивлениях амплитудой милливольт на И индуктивностях сотни проводников. В результате, генерируемый на проводниках питания шум требует повышенного внимания, чтобы исключить его влияние на качество работы ЦАП. Хорошее решение – использовать для подачи питания на ЦАП специально выделенные проводники питания и земли с хорошей фильтрацией.

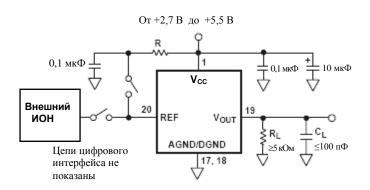

ЦАП 1273ΠA2T, Для питания 1273ΠA2AT следует использовать проводники, трассированные непосредственно от системного источника питания. Такое включение показано на рисунке 7. Здесь используется LC-фильтр и выделенные проводники для напряжения питания и земли, что позволяет изолировать переходных процессов, аналоговые цепи OTинициируемых переключающими логическими схемами.

Подп. и дата

Инв. № дубл.

윋

Взам. Инв.

Рисунок 7 - Использование отдельных линий питания для уменьшения шума на линиях питания ЦАП

В любом случае, используются отдельные линии для питания ЦАП или нет, «обильная» фильтрация будет улучшать качество питания. Рекомендуется, также, локальная фильтрация (непосредственно около микросхемы, как показано на рисунке 8): танталовый электролитический конденсатор емкостью 10 мкФ параллельно с керамическим конденсатором 0,1 мкФ.

Рисунок 8 - Рекомендуемая схема локальной фильтрации питания ИС 1273ПА2Т, 1273ПА2АТ

### 5.6 Входные каскады цифровых сигналов

Подп. и дата

Инв. № дубл.

윋

Взам. Инв.

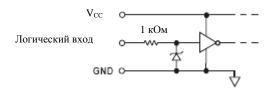

Все цифровые логические входы ИС имеют защиту от электростатического разряда (ESD) с использованием стабилитрона, как показано на рисунке 9.

Рисунок 9 — Эквивалентная схема цифрового входа ИС с обеспечением защиты от статического электричества

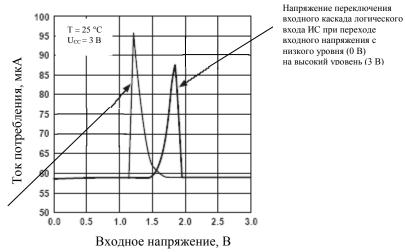

Для уменьшения потребляемой мощности микросхемой при входных логических уровнях, близких к уровням U<sub>IH</sub> и U<sub>IL</sub>, заданным в таблице 2, в схемах цифровых входов применены триггеры Шмитта. Применение триггеров Шмитта уменьшает ток потребления входными буферными каскадами по сравнению с традиционными входными каскадами КМОП-схем. На рисунке 10 приведен график зависимости потребляемого тока от величины входного напряжения. Из графика видно, что ток потребления незначителен, когда уровни входных сигналов статичны. Небольшие всплески наблюдаются в моменты переключений уровней. Имеется ещё одно преимущество у входных каскадов со встроенными триггерами Шмитта — они предотвращают ложные переключения, которые характерны для стандартных КМОП логических интерфейсов и оптоэлектронных схем, если входной сигнал представляет собой медленно изменяющийся логический переход. Все логические входы микросхемы: DIN0 — DIN11, CS#, RS#, SHDN# содержат триггеры Шмитта.

Напряжение переключения входного каскада логического входа ИС при переходе входного напряжения с высокого уровня (3 В) на низкий уровень (0 В)

Подп. и дата

Инв. № дубл

윋

Взам. Инв.

Подп. и дата

№ подп

Рисунок 10 – Зависимость потребляемого тока от величины входного напряжения

## 5.7 Цифровой интерфейс

ИС 1273ПА2Т, 1273ПА2АТ имеют параллельный интерфейс на входе. Функциональная схема цифровой части микросхем показана на рисунке 11.

Рисунок 11 - Функциональная схема цифровой части ИС

Таблица истинности функционирования входной цифровой части дана в таблице 4. Сигнал выбора кристалла CS# управляет загрузкой данных с линий DIN0 – DIN11. Активный низкий уровень сигнала CS# переводит входной регистрзащелку в состояние, когда он пропускает входные данные к резисторной матрице ЦАП без изменений. Когда сигнал CS# возвращается на высокий уровень, входные данные фиксируются В регистре-защелке. При ЭТОМ данные должны устанавливаться и удерживаться на линиях данных относительно нарастающего фронта в соответствии с требованиями к параметрам «время установления» и «время удержания».

## 5.8 Сигнал сброса RS#

Подача на вход RS# низкого уровня записывает во все триггеры входного регистра ЦАП нули - напряжение на выходе ЦАП становится равным 0 В. Функция сброса ЦАП может использоваться для установки ЦАП в состояние «0» после включения питания и (или) после сбоя по питанию. Установка ЦАП в определенное известное состояние при включении питания — это полезная функция во многих применениях. Тестовые системы и контроллеры двигателей — два из них. Сигнал сброса может вырабатываться микропроцессором при включении питания или формироваться внешней цепочкой RC.

№ подл.

В цепи входного сигнала RS# имеется триггер Шмитта, который обеспечивает нормальное функционирование входа при медленно изменяющемся входном сигнале.

#### 5.9 Дежурный режим (сигнал SHDN#)

Подп. и дата

Инв. № дубл.

Взам. Инв. №

№ подл.

Дежурный режим предназначен для максимального энергосбережения. Этот режим вводится при подаче низкого уровня напряжения на вход SHDN#. Цепь сигнала SHDN# включает в себя триггер Шмитта, что позволяет подавать на этот вход медленно изменяющиеся сигналы. При подаче низкого уровня на вход SHDN#, потребление ИС 1273ПА2Т, 1273ПА2АТ падает до уровня наноампер. Потребление тока в полном диапазоне допустимых температур не превышает 1,5 мкА. Если напряжение питания не снимается с микросхемы все время, пока она находится в дежурном режиме, то внутренний регистр ЦАП сохраняет последние записанные в него данные. В дежурном режиме цифровой интерфейс сохраняет свою активность так, что измененный код вызовет установление выходного сигнала ЦАП в соответствии с новым кодом после возврата ИС из дежурного режима.

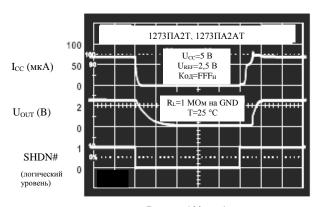

На рисунке 12 показана осциллограмма выхода ИС из дежурного режима с демонстрацией тока потребления и выходного напряжения.

Время – 100 мкс/деление

Рисунок 12 - Осциллограмма тока потребления и выходного напряжения ИС при выходе из дежурного режима

В дежурном режиме выходной усилитель напряжения проявляет себя как разомкнутая цепь с высоким сопротивлением. На любой нагрузке, подключенной к выходу ЦАП, будет удерживаться её собственный потенциал. Если пользователь не предполагает включать дежурный режим, то вывод SHDN# следует подключить к выводу  $V_{CC}$ , что блокирует возможность входа в дежурный режим.

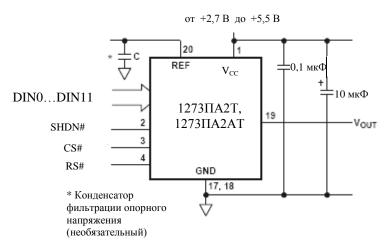

#### 5.10 Использование микросхем в однополярном режиме работы

Это основной режим работы микросхем. Схема включения ИС в однополярном режиме показана ниже. Как видно из схемы (см. рисунок 13), нагрузка микросхемы менее 5 кОм (резистивная) и более 100 пФ (емкостная) не допустима. В таблице 5 приведены некоторые входные ключевые коды и соответствующие им выходные напряжения.

Схема может использовать отдельные источники опорного напряжения и питания, а может использовать один источник напряжения и для питания, и как опорный, в зависимости от предъявляемых к ЦАП требований.

Подп. и дата

Инв. № дубл.

Взам. Инв. №

Подп. и дата

Рисунок 13 — Схема включения микросхем 1273ПА2T, 1273ПА2AT в однополярном режиме

Таблица 5 — Некоторые входные коды и соответствующие выходные напряжения в однополярном режиме

| Шестнадцатиричное число | Десятичное число | Выходное напряжение, В |

|-------------------------|------------------|------------------------|

| в регистре ЦАП          | в регистре ЦАП   | при $U_{REF} = 2,5 B$  |

| FFF                     | 4095             | 2,4994                 |

| 801                     | 2049             | 1,2506                 |

| 800                     | 2048             | 1,2500                 |

| 7FF                     | 2047             | 1,2494                 |

| 000                     | 0                | 0                      |

#### 5.11 Использование микросхем в биполярном режиме работы

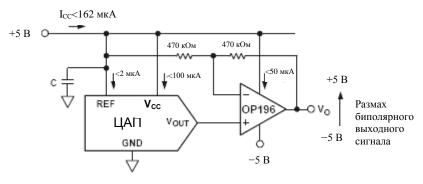

Хотя микросхемы 1273ПА2Т, 1273ПА2АТ разработаны для одного источника питания, выходной сигнал ИС легко преобразовать для реализации биполярного режима с помощью добавления одного операционного усилителя. На рисунке 14 приведена схема реализации биполярного режима на базе ИС 1273ПА2Т

Примечание – В схеме для простоты не показан цифровой интерфейс

Рисунок 14 - Схема реализации биполярного режима

Схема использует для питания хорошо стабилизированный качественный источник напряжения 5 В, который также обеспечивает ЦАП опорным напряжением. Поскольку, размах выходного напряжения ЦАП: от 0 В до напряжения близкого к 5 В, то следует использовать операционный усилитель, у которого входной диапазон синфазного напряжения распространяется до напряжения положительного питания. Микромощный операционный усилитель типа ОР196 является подходящим для этой цели. Его максимальный потребляемый

ток — всего 50 мкА. Применение резисторов одного номинала 470 кОм дает коэффициент усиления каскада на ОУ ОР196 равный двум. В результате, размах напряжения на выходе схемы равен десяти вольтам (от минус 5 В до 5В). При подаче на вход последовательно нарастающих кодов от  $000_{\rm H}$  — нуля шкалы до  $800_{\rm H}$  — середины шкалы и, далее, до FFF<sub>H</sub> — полной шкалы, выходное напряжение будет изменяться от минус 5 В до (плюс 5 В — 1МР3). Выходное напряжение определяется следующим выражением

$$V_0 = (D/2048 - 1) \times 5$$

,

где D – десятичное значение двоичного кода, загруженного в регистр ЦАП. Следует отметить, что величина MP3 в этом случае равна 10/4096=2,44 мВ.

Примененные резисторы 470 кОм обеспечивают минимальное потребление мощности. Резисторы должны быть с малым температурным коэффициентом для поддержания точности И должны быть строго равны ПО номиналам (предпочтительнее изготовленные по одной технологии, например, металлопленочные). Если требуется более высокая стабильность, то в качестве источника питания следует применить прецизионный источник опорного напряжения, например, источник типа REF195, который в состоянии легко обеспечить необходимый для ЦАП ток 162 мкА и дополнительный ток для нагрузки, Прецизионный типа REF196 подключаемой к выходу схемы. источник гарантирует вытекающий ток 10 мА при собственном потреблении 50 мкА.

В таблице 6 приведены номинальные выходные напряжения, вырабатываемые схемой, показанной на рисунке 14 для некоторых ключевых значений входного кода.

Таблица 6

| Шестнадцатиричное    | Десятичное число в | Выходное напряжение,    |

|----------------------|--------------------|-------------------------|

| число в регистре ЦАП | регистре ЦАП       | $B$ при $V_{REF} = 5 B$ |

| FFF                  | 4095               | 4,99756                 |

| 801                  | 2049               | 0,00244                 |

| 800                  | 2048               | 0,00000                 |

| 7FF                  | 2047               | -0,00244                |

| 000                  | 0                  | -5,00000                |

# Лист регистрации изменений

|              | Изм. | Номера листов (страниц) |                          |       |                     | Всего листов |                   | Входящий №<br>сопроводи-        |       |          |

|--------------|------|-------------------------|--------------------------|-------|---------------------|--------------|-------------------|---------------------------------|-------|----------|

|              |      | изме-<br>нённых         | заме-<br>нённых          | новых | аннули-<br>рованных | (страниц)    | №<br>документа    | тельного<br>документа<br>и дата | Подп. | Дата     |

|              | 1    | 1, 2                    | 3-11,<br>14-17,<br>19-21 | -     | -                   |              | ГКДЯ.009-<br>2011 | -                               |       | 25.04.11 |

|              |      |                         |                          |       |                     |              |                   |                                 |       |          |

|              |      |                         |                          |       |                     |              |                   |                                 |       |          |

| Подп. и дата |      |                         |                          |       |                     |              |                   |                                 |       |          |

| Инв. № дубл. |      |                         |                          |       |                     |              |                   |                                 |       |          |

| Взам. Инв. № |      |                         |                          |       |                     |              |                   |                                 |       |          |

| Подп. и дата |      |                         |                          |       |                     |              |                   |                                 |       |          |